M11L416256A-25T

| Model | M11L416256A-25T |

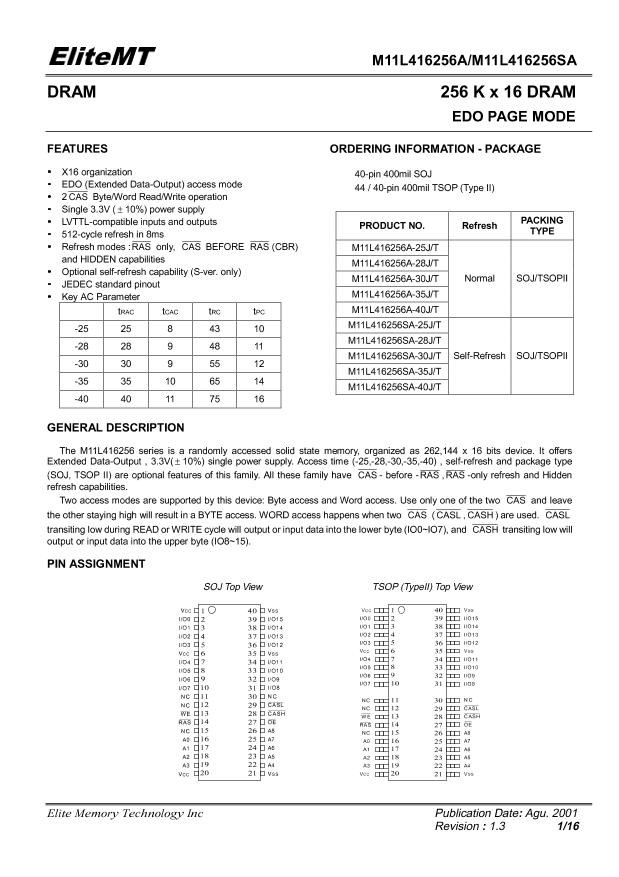

| Description | EDO DRAM, 256KX16, 25ns, CMOS, PDSO40, TSOP2-44/40 |

| PDF file | Total 16 pages (File size: 231K) |

| Chip Manufacturer | ESMT |

(OLWH07

CAPACITANCE

(Ta = 25

°

C , V

CC

= 3.3V

±

10%)

PARAMETER

Input Capacitance (address)

Input Capacitance (

RAS

,

CASH

,

CASL

,

WE

,

OE

)

Output capacitance (I/O0~I/O15)

SYMBOL

C

I1

C

I2

C

I / O

-

-

-

M11L416256A/M11L416256SA

TYP

MAX

5

7

10

UNIT

pF

pF

pF

AC ELECTRICAL CHARACTERISTICS

(Ta = 0 to 70

°

C , V

CC

=3.3V

±

10%, V

SS

= 0V) (note 14)

Test Conditions

Input timing reference levels : 0.8V, 2.0V

Output reference level : V

OL

= 0.8V, V

OH

=2.0V

Output Load : 2TTL gate + CL (50pF)

Assumed t

T

= 2ns

PARAMETER

Read or Write Cycle Time

Read Write Cycle Time

EDO-Page-Mode Read or Write Cycle

Time

EDO-Page-Mode Read-Write Cycle

Time

Access Time From

RAS

Access Time From

CAS

Access Time From

OE

Access Time From Column Address

Access Time From

CAS

Precharge

SYMBOL

t

RC

t

RWC

t

PC

t

PCM

t

RAC

t

CAC

t

OAC

t

AA

t

ACP

t

RAS

t

RASC

t

RSH

t

RP

t

CAS

t

CSH

t

CP

t

RCD

t

CRP

t

ASR

t

RAH

t

RAD

t

ASC

t

CAH

t

AR

t

RAL

t

RCS

-25

-28

-30

-35

-40

MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX

43

65

10

32

25

8

8

12

14

25

25

8

15

4

21

4

10

5

0

5

8

0

5

22

12

0

13

17

10K

10K

100K

28

28

9

17

5

24

4

10

5

0

5

8

0

5

24

15

0

13

19

10K

48

70

11

35

28

9

9

15

17

10K

100K

30

55

85

12

37

30

9

9

15

17

10K

35

65

95

14

42

35

10

10

18

20

10K

100K

40

75

105

16

47

40

11

11

20

22

10K

UNIT NOTES

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

20

22

22

4

5,20

13,20

RAS

Pulse Width

RAS

Pulse Width (EDO Page Mode)

RAS

Hold Time

RAS

Precharge Time

CAS

Pulse Width

CAS

Hold Time

CAS

Precharge Time

RAS

to

CAS

Delay Time

CAS

to

RAS

Precharge Time

Row Address Setup Time

Row Address Hold Time

30 100K 35

9

20

5

26

4

10

5

0

5

8

0

5

26

15

0

15

21

10K

10

25

5

30

5

10

5

0

5

8

0

5

30

18

0

40 100K ns

11

30

ns

ns

10K

ns

ns

ns

29

ns

ns

ns

ns

20

ns

ns

ns

ns

ns

15,18

25

10K

6

35

5

24

19

6,23

7,18

19

25

10

5

0

5

RAS

to Column Address Delay Time

Column Address Setup Time

Column Address Hold Time

Column Address Hold Time (Reference

to

RAS

)

Column Address to

RAS

Lead Time

Read Command Setup Time

17

8

0

5

34

20

0

8

18

18

Elite Memory Technology Inc

Publication Date: Agu. 2001

Revision

:

1.3

4/16